「BUAA CO」P5总结

主要任务

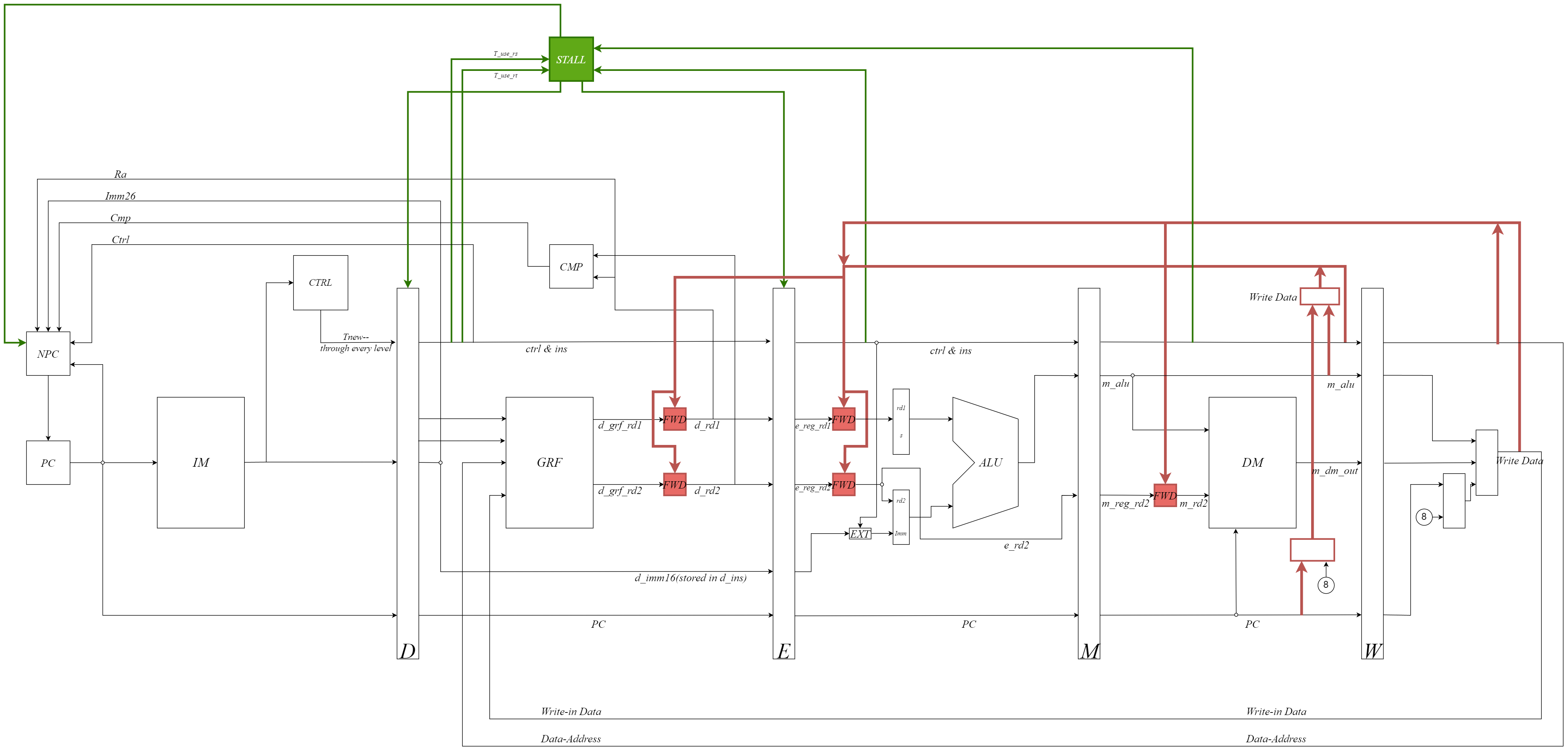

顶层设计

其中红色为转发有关设计、绿色为阻塞有关设计

建议

P5是一个难点,代码量也比P4要多很多,很容易挂或者Gap,建议合理分配时间。

注意事项

1. 集中式译码和分布式译码

集中式译码将控制信号集中译码出来,再逐级流水;而分布式译码在每一级都设置译码单元,将该流水级需要使用的控制信号译码出来。我在P5的设计中采用了集中式译码,但是经历了P7之后,个人认为分布式译码方便不止一点点。

集中式译码的控制信号表示

由于集中式译码会一次性产生大量控制信号,需要为每一个控制信号专门在流水级分配一个寄存器。但是这种方式太麻烦,因此可以规定控制信号的排列顺序,用vector将控制信号合并一同传递。这种方式的缺点是可读性低,每次都需要查询控制信号的某一位对应的是什么控制信号。因此我在mips.v文件的开头将控制信号全部用wire类型变量接了出来,使得还不如直接分布式译码。

个人认为集中式译码的一个好处在于可以将控制信号流水。这意味着如果某一流水级的结果对后续流水级造成影响时,可以通过改变传递给下一流水级的控制信号来实现。但是分布式译码的结果直接取决于指令本身。

举个例子,比方说写入寄存器的reg_write控制信号,描述了一条指令是否需要写入寄存器。指令beqal $t0, $t1, TARGET表示如果$t0和$t1相等,则跳转到TARGET并链接(将当前PC写入$31)。这时候分布式译码无法根据指令本身判断reg_write的值,因此指令在W级时需要保留D级CMP模块的比较结果,因此需要额外流水D级CMP比较结果。但是集中式译码只需要根据D级的比较结果选择指定信号传递给E级的reg_write就行。

在之后的设计中,流水数据或信号是很常见的,也并不困难。因此集中式译码的上述优势并不显著。在P7的异常判断中,分布式译码会表现出一定的优势所以我将分布式和集中式进行了混搭。建议分布式译码。

2.

不能减为负数,在一些设计中可能会出问题。 时可以视为这条指令不会写入寄存器; 可以视为这条指令不会使用到寄存器。 可以用 的任何一个数去表示,因为 时在W流水级及之后不会有任何接受转发的位点。

3. 转发

2023计组课程组要求能转发尽量转发。但是这个要求是针对P5课下而言的。在P7的eret的实现中可以阻塞也可以转发。

转发位置

转发位点见顶层设计图。

转出位点有:

- W级写入数据

- M级写入数据

接受转发位点有:

- M级DM的地址

- E级的两个操作数

- D级GRF(内部转发)

转发要求从流水寄存器转发,这样能够缩短流水级的关键路径,使得时钟周期不会因为转发而增加太多,甚至是不增加。

我在设计的过程中并没有使用内部转发,而是改成了向D级转发。效果完全相同,不过不建议这么做

转发条件

接受转发时先接受M级转发在接受W级转发。

实现方式

可以用分布式的转发模块对转发进行管理,也可以使用一个集中转发控制模块对全部转发任务进行控制。我选择了前者,在每一个转发位点实例化了一个_FWD模块对该位点是否接受转发进行判断然后被助教骂了一顿。

4. 暂停

阻塞位置

全部指令需要阻塞在D级,也就是说包括D级在内的所有流水级都要冻住,E级流水寄存器要产生空泡。具体来说,暂停信号作用的地方有

- D级流水寄存器,使之不更新

- PC,使之不更新(或者NPC,使之等于PC)

- E级流水寄存器,使之产生空泡

阻塞条件

关于空泡

空泡的PC建议保留为被阻塞指令的PC,比方说beq被阻塞在D级,那么E级产生的空泡的PC就保持和beq的PC相同。这在P7中会用到,不过也可以等到P7再改。

5. 关于冲突

课上学习我们了解到,冲突有三种,其中结构冲突通过我们的哈佛结构CPU已经解决,控制冲突在MIPS中是通过延迟槽解决的,而数据冲突的三种类型(WAW, RAW, WAR)中,只有写后读(RAW)需要我们操心。WAW在我们的流水线中几乎不会产生影响,这是因为我们一个时钟周期只会对同一个存储设备的同一个位置进行一次写入;WAR也不会有什么问题,在我们的设计中,写操作并不会对读操作带来多大的干扰,如果非要说,就是内部转发解决了这个冲突。

祝P5一切顺利!

- 标题: 「BUAA CO」P5总结

- 作者: Squirrel7ang

- 创建于 : 2024-01-02 22:12:14

- 更新于 : 2024-02-01 20:18:30

- 链接: https://redefine.ohevan.com/2024/01/02/CO/P5/

- 版权声明: 本文章采用 CC BY-NC-SA 4.0 进行许可。